### FB2M5KRR

## 10/100/250 Mbps Fiber Optic OptoLock<sup>®</sup> Transceiver for 2.2 mm POF with RSSI Output

Data Sheet

Firecomms' plugless OptoLock® transceiver features a small form factor housing containing a pair of integrated transmitter and receiver optoelectronic components designed for efficient coupling to Plastic Optical Fiber (POF). This port for bare fiber significantly simplifies the optical connection, (no plug required) thus reducing installation and maintenance time for industrial, medical and consumer applications.

The OptoLock<sup>®</sup> offers a compact device supporting Fast Ethernet, Industrial Ethernet (e.g. EtherCAT and Sercos III) and proprietary data links running data from 10 Mbps to 250 Mbps. It is compatible with the 200 Mbps (8B/10B) port on many FPGA and ASIC devices.

The OptoLock<sup>®</sup> can be interfaced to a variety of lowvoltage differential data buses such as LVDS, LVPECL and CML.

For low power designs the transceiver provides an electrical power saving feature. If no data or toning inputs are present on the input bus, the transmitter will enter a sleep state and the Resonant Cavity LED (RCLED) is switched off. Similarly, with no optical signal present, the receiver will switch into a sleep mode. In sleep mode the total current consumption is reduced to a typical value of 27  $\mu$ A. The receiver also features a Received Strength Signal Indicator (RSSI) function to monitor the 'health' status of the link.

OptoLock\* is protected by U.S. patents 7,597,485 and 7,905,665 and Chinese patents 101501545 A and 102135650 B.

#### **AVAILABLE OPTIONS**

# Table 1 ORDERING INFORMATION / PART NUMBER

Industrial OptoLock<sup>®</sup> Transceiver with RSSI, 2.2 mm POF, Black

#### **FEATURES**

- Simple low-cost termination solution for 2.2 mm jacketed POF cables without a plug

- Compatible with 8B/10B encoding schemes -250 Mbps is the maximum NRZ symbol rate

- RSSI output function from receiver

- Resonant Cavity LED (RCLED) at red 650 nm with small emission aperture suitable for POF

- Integrated CMOS driver IC for RCLED

- High sensitivity single chip CMOS receiver IC with integrated PIN diode for robust EMI/EMC performance

- Integrated optics for efficient coupling to 0.5 NA POF

- Low power consumption with power saving features

- -40 °C to +85 °C operating range

- RoHS compliant

#### APPLICATIONS

| Table 2<br>APPLICATIONS                                                                           |

|---------------------------------------------------------------------------------------------------|

| Industrial and robotic Links                                                                      |

| 200 Mbps 8B10B serial<br>communications. 100Base-Fx fiber<br>based Ethernet, EtherCAT, Sercos III |

| 50 m over Step Index POF <sup>[1]</sup> at 250 Mbps                                               |

| 250 Mbps                                                                                          |

|                                                                                                   |

Note: 1. Maximum link lengths will vary with installation conditions and operating data rate.

#### **SPECIFICATIONS**

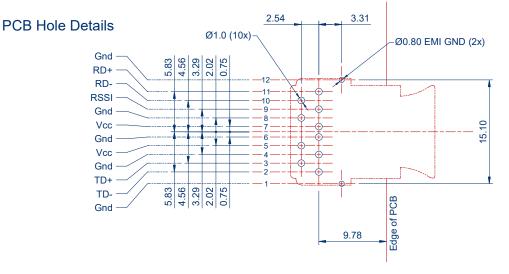

## Table 3TRANSCEIVER PIN DESCRIPTION

| Pin | Name                      | Symbol |

|-----|---------------------------|--------|

|     | Transmitter               |        |

| 1   | EMI Shield <sup>[1]</sup> | SHIELD |

| 2   | Signal Input (Negative)   | TD-    |

| 3   | Signal Input (Positive)   | TD+    |

| 4   | Ground Pin <sup>[1]</sup> | GND    |

| 5   | DC Power Input Pin 3.3 V  | Vcc    |

| 6   | Ground Pin <sup>[1]</sup> | GND    |

|     | Receiver                  |        |

| 7   | DC Power Input Pin 3.3 V  | Vcc    |

| 8   | Ground Pin <sup>[1]</sup> | GND    |

| 9   | RSSI                      | RSSI   |

| 10  | Data Output (Negative)    | RD-    |

| 11  | Data Output (Positive)    | RD+    |

| 12  | EMI Shield <sup>[1]</sup> | SHIELD |

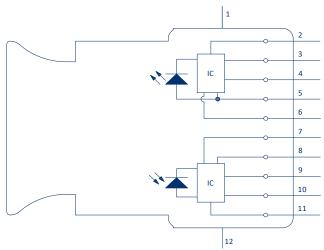

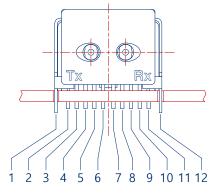

FIGURE 1 Transceiver pin-out numbering scheme, top view shown.

1. Note that the EMI Shield ground pins should be connected to the signal ground plane on the PCB. This is important to prevent cross-talk between Transmitter and Receiver and also to shield the FOTs from external EMI/EMC and ESD.

#### **ELECTRICAL INTERFACE**

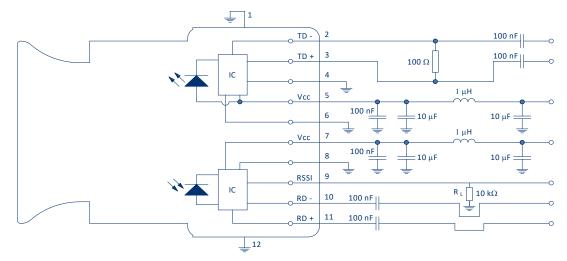

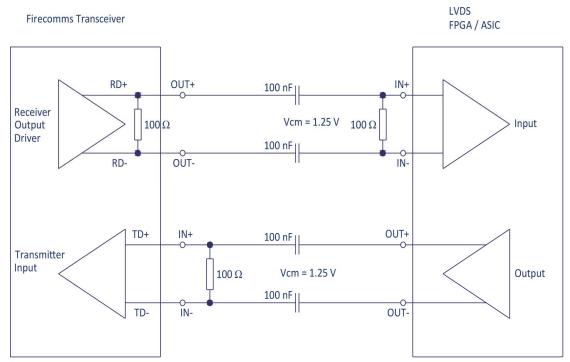

#### FIGURE 2

General application circuit schematic to AC couple to Firecomms transceiver.

#### Notes:

- 1. The transmitter and receiver are shielded from each other to prevent crosstalk. To be effective this shield must be grounded.

- 2. Both GND Pins of the Transmitter FOT must be connected to GND (they are not connected internally).

- 3. Power line capacitors should be located as close as possible to the FOTs' DC Power Input Pins.

- 4. The data lines are impedance-matched differential pairs. The PCB layout for these tracks must comply to IEEE standards for highspeed data and impedance matching. The 100 nF coupling capacitors are sized for high speed data (10 to 250 Mbps).

- 5. The Receiver data output pins RD + and RD are internally terminated to  $100 \Omega$ .

- 6. The TD + and TD do not have internal termination and must be externally terminated with a 100  $\Omega$  resistor.

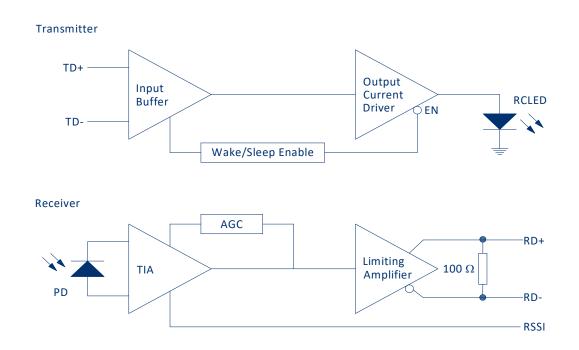

#### ELECTRONIC BLOCK DIAGRAM

FIGURE 3 Electronic block diagrams of the Transmitter and Receiver fibre optic transceivers.

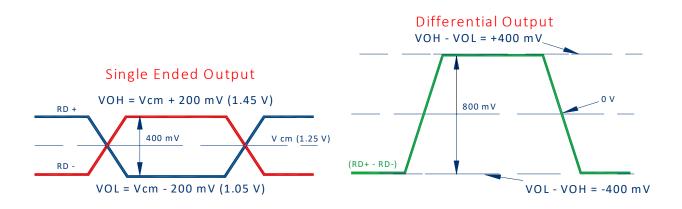

FIGURE 4

On the left the Optical Receiver Output voltage swing as measured from each output (single ended) and on the right as the differential measurement across both outputs.

The precise VOH and VOL values depend critically on the common mode DC level. In LVDS applications this is 1.25 V. In LVPECL it is 2 V and in CML it is 1.5 V. The following application circuits illustrate how the Firecomms part can be used with LVPECL, LVDS and CML interfaces generally found on Ethernet PHY, FPGA and ASIC devices. The specific circuit for an individual manufacturer sometimes differs from these general guidelines. Please contact Firecomms for assistance with specific ICs.

#### APPLICATION CIRCUIT FOR AN LVDS INTERFACE

#### FIGURE 5

This is the general AC coupled LVDS interface circuit for the Firecomms transceiver. It assumes that the LVDS device (FPGA or ASIC) does not have internal termination. Both Optical transmitter and receiver require a common mode voltage of 1.25 V for optimum operation.

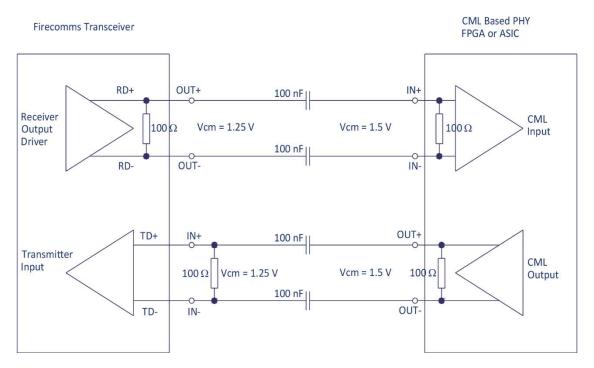

#### **APPLICATION CIRCUIT FOR A CML INTERFACE**

#### FIGURE 6

This is the general AC coupled CML interface circuit for the Firecomms transceiver. It assumes that the CML device has internal termination. The CML side of the coupling capacitors has a common mode voltage of 1.5 V.

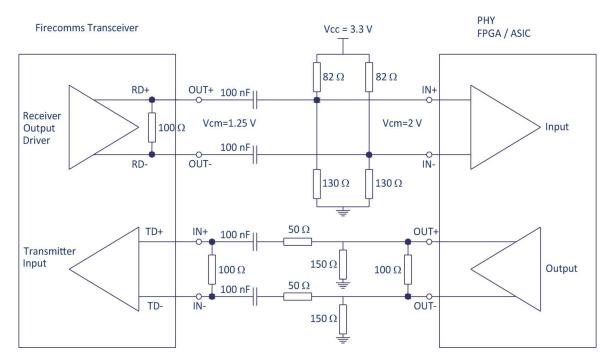

#### APPLICATION CIRCUIT FOR AN LVPECL INTERFACE

FIGURE 7

This is the general AC coupled LVPECL interface circuit for the Firecomms transceiver. It assumes that the PHY/FPGA/ASIC device does not have internal termination. The resistor network sets the Common mode voltage of 2 V for the LVPECL application circuit.

The Firecomms transceiver can be interfaced to standard LVPECL devices such as 100 Mbps Fast Ethernet PHY ICs. AC coupling is important to ensure the correct common mode voltage. The optical receiver is a CMOS device and its output stage has a common mode of 1.25 V. By AC coupling this to a standard LVPECL resistor network ( $82/130 \Omega$ ) the common mode is shifted to 2 V and the correct VOH to VOL voltage swing is achieved.

The 100 nF AC coupling capacitors are ideal for high speed operation (100 to 200 Mbps). For lower data rates these should be increased as appropriate.

As Ethernet PHY ICs often differ in the design of their interface circuits, it is recommended that the user contact Firecomms application support who can advise on the exact circuit that will work best with leading PHY suppliers, for example Micrel/Microchip, Marvell, Realtek, TI and IC Plus.

Firecomms can also provide support with interfaces to FPGAs from Xilinx, Altera, Lattice and others.

Care must be taken during the layout of the PCB to use best practice for high-speed signaling. Place bypass capacitors as close as possible to the transceiver. Use a continuous low-inductance ground plane and controlled impedance traces for the data lines.

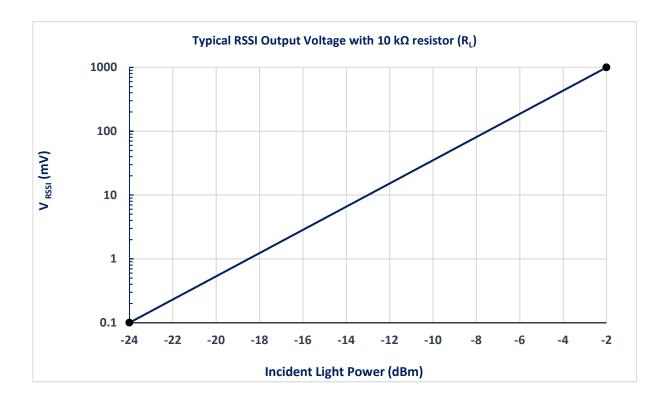

#### RSSI

This OptoLock<sup>®</sup> transceiver provides a Received Signal Strength Indicator (RSSI) current output from the receiver. The RSSI output indicates the Average Optical Power (AOP) falling on the receiver. This RSSI signal therefore provides a health status indication that can be communicated to the user and wider network. To use the RSSI output, place a resistor (R<sub>L</sub>) between RSSI pin and ground to generate  $V_{RSSI}$  analogue voltage;  $V_{RSSI}$  is proportional to the AOP. This  $V_{RSSI}$  output can then be used as an input into a signal monitoring circuit.

#### FIGURE 8

A graph of the Voltage ( $V_{RSSI}$ ) generated across the RSSI resistor ( $R_L$ ) versus the light power incident on the photodiode as per the circuit shown in Figure 2.

#### **SPECIFICATIONS**

#### Table 4 REGULATORY COMPLIANCE

| Parameter                                        | Symbol | Standard             | Level                  |

|--------------------------------------------------|--------|----------------------|------------------------|

| Storage Compliance                               | MSL    | J-STD-020            | 2a (4-week floor life) |

| Restriction of Hazardous<br>Substances Directive | RoHS   | Directive 2011/65/EU | Certified compliant    |

| Eye Safety                                       |        | IEC 60825-1          | LED Class 1            |

#### Table 5 ABSOLUTE MAXIMUM RATINGS

These are the absolute maximum ratings at or beyond which the component can be expected to be damaged Notes:

1. 260 °C for 10 seconds, one time only, at least 2.2 mm away from lead root

| Parameter                 | Symbol           | Minimum | Maximum             | Unit |

|---------------------------|------------------|---------|---------------------|------|

| Storage Temperature       | T <sub>stg</sub> | -40     | +85                 | °C   |

| Operating Temperature     | T <sub>op</sub>  | -40     | +85                 | °C   |

| Soldering Temperature [1] | T <sub>sld</sub> |         | +260 <sup>[1]</sup> | °C   |

| Supply Voltage            | V <sub>R</sub>   | -0.5    | 3.6                 | V    |

#### TRANSMITTER ELECTRICAL AND OPTICAL CHARACTERISTICS

Test Conditions:

1. Test data was validated over the full temperature range of -40  $^\circ$ C to +85  $^\circ$ C, and over the supply range of 3 V to 3.6 V

2. Test data represents operation at the maximum data rate of 250 Mbps using a PRBS7 test pattern unless otherwise stated

3. Optical power is measured when coupled into 0.5 m of a 1 mm diameter 0.5 NA POF

| Parameter                                               | Symbol                | Min     | Typical | Max                  | Unit | Test Condition       |

|---------------------------------------------------------|-----------------------|---------|---------|----------------------|------|----------------------|

| DC Supply Voltage                                       | Vcc                   | 3.0     | 3.3     | 3.6                  | V    | [1,2]                |

| Operating Current Consumption                           | lcc                   |         | 37      | 52                   | mA   | [1]                  |

| Sleep State Current Consumption                         | I <sub>Sleep</sub>    |         | 20      | 40                   | μA   | < 30 dBm of<br>Light |

| Data Rate                                               | Baud Rate             | 10      |         | 250                  | Mbps | [1,2]                |

| Data Input Capacitance                                  | C <sub>IN</sub>       |         |         | 5                    | pF   | [1]                  |

| Data Input Resistance<br>(Single-Ended)                 | R <sub>IN</sub>       |         | 5       |                      | kΩ   | [1]                  |

| Input Common-Mode Range                                 | V <sub>IN-BIAS</sub>  | GND+0.8 |         | V <sub>CC</sub> -0.8 | V    | [1,2]                |

| Input Voltage Swing                                     | V <sub>IN-SWING</sub> | 100     |         | 1200                 | mV   | [1,2]                |

| Minimum Differential Voltage<br>Swing to Ensure Wake-Up | Wake-up<br>Input      | 50      |         |                      | mV   | [1]                  |

| Wake-Up Time Delay                                      | T <sub>WU</sub>       |         | 5       | 80                   | μs   | [1]                  |

| Optical Power OFF Delay                                 | T <sub>OD</sub>       | 0.02    |         | 20                   | μs   | [1,3]                |

| Peak Wavelength                                         | $\lambda_{peak}$      | 640     | 660     | 670                  | nm   | [3]                  |

| Spectral Bandwidth (FWHM)                               | Δλ                    |         | 23      | 30                   | nm   | [3]                  |

| Average Optical Power                                   | Р                     | -10     |         | -2.0                 | dBm  | [3]                  |

| Optical Rise Time (20 % - 80 %)                         | t <sub>R</sub>        |         | 2.0     | 2.8                  | ns   | [1,2,3]              |

| Optical Fall Time (20 % - 80 %)                         | t <sub>F</sub>        | 0.3     |         | 0.6                  | ns   | [1,2,3]              |

| Optical Modulation Amplitude                            | OMA                   | 160     | 590     | 1250                 | μW   | [1]                  |

| Total Jitter                                            | J <sub>TOT</sub>      |         |         | 1.6                  | ns   | [1,2]                |

Table 7 RECEIVER ELECTRICAL AND OPTICAL CHARACTERISTICS

Test Conditions:

1. Test data was validated over the full temperature range of -40  $^{\circ}$ C to +85  $^{\circ}$ C, and over the supply range of 3 V to 3.6 V

2. Test data represents operation at the maximum data rate of 250 Mbps using a PRBS7 test pattern unless otherwise stated

3. Optical power was coupled from a minimum 0.5 m length of 1 mm diameter core and 0.5 NA step index POF

4. Measured by an oscilloscope with AC Coupled 50 Ohm termination for each data input line or using a 100 Ohm terminated differential probe with minimal capacitance

5. Typical Ethernet applications will run at 100 Mbps of 4B5B encoded data which is equivalent to a symbol rate of 125 MBd

6. Typical FPGA applications will run at 200 Mbps of 8B10B encoded data which is equivalent to a symbol rate of 250 MBd

| Parameter                             | Symbol                             | Min  | Typical | Max            | Unit | Test Condition              |

|---------------------------------------|------------------------------------|------|---------|----------------|------|-----------------------------|

| DC Supply Voltage                     | Vcc                                | 3.0  | 3.3     | 3.6            | V    | [1]                         |

| Data Rate                             | BR                                 | 10   |         | 250            | Mbps | See encoding<br>[2],[5],[6] |

| Operating Current Consumption         | lcc                                | 18   | 22      | 30             | mA   | [1,2,]                      |

| Sleep State Current Consumption       | ls                                 | 2    | 7       | 15             | μA   | [1,2]                       |

| Output Impedance Between RD+ and RD - | Z <sub>DIFF</sub>                  |      | 100     |                | Ohm  | [1,2,4]                     |

| Offset Common Mode Voltage            | V <sub>ocm</sub>                   | 1.15 | 1.25    | 1.35           | V    | [1,2,4]                     |

| Output Voltage peak-peak swing        | V <sub>O-pp</sub>                  | 325  | 400     | 500            | mV   | [4]                         |

| Differential Voltage Output Swing     | V <sub>diff</sub>                  | 650  | 800     | 1000           | mV   | [4]                         |

| Receivable Optical Power Sensitivity  | P <sub>IN</sub>                    |      |         | -24            | dBm  | [3]                         |

| Maximum Allowed Optical Power         | P <sub>OL</sub>                    |      |         | -2             | dBm  | [3]                         |

| Rise Time (10 % - 90 %)               | t <sub>R</sub>                     |      | 0.4     | 1              | ns   | [1,3]                       |

| Fall Time (90 % - 10 %)               | t <sub>F</sub>                     |      | 0.4     | 1              | ns   | [1,3]                       |

| Optical Power to enter Sleep          | P <sub>SL</sub>                    | -40  | -31     | -              | dBm  | [1,3]                       |

| Optical Power to wake from Sleep      | P <sub>WU</sub>                    |      | -28     | -26            | dBm  | [1,3]                       |

| Sleep State Delay                     | T <sub>SD</sub>                    |      | 2       |                | S    |                             |

| Wake Up Time from Sleep State         | T <sub>WU-SLEEP</sub>              |      | 100     |                | μs   |                             |

| Receiver Jitter                       | J <sub>TOT</sub>                   |      |         | 1.5            | ns   | Ideal input<br>signal       |

| Voltage at RSSI                       | V <sub>RSSI</sub>                  | 0    |         | $V_{CC} - 1.5$ | V    |                             |

| RSSI Output Responsivity              | I <sub>RSSI</sub> /P <sub>IN</sub> |      | 0.16    |                | A/W  | [3]                         |

#### **MECHANICAL DATA**

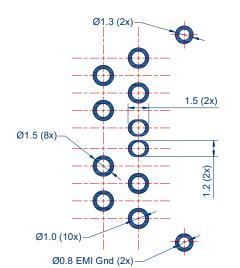

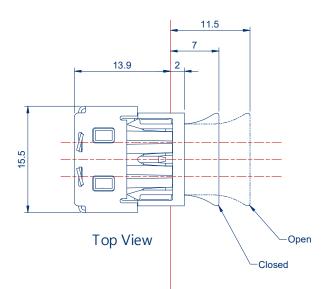

#### FIGURE 9

Mechanical dimensions of the product, and PCB footprint, which is a top view. General dimensional tolerance is ± 0.2 mm.

NOTE: For PCB layout extra care is required with pin 6 and pin 7. On the PCB top and bottom metal pin 6 and pin 7 require a non-circular pad. The VIAs are standard plated circular through holes, however, the VIA top and bottom solder pad areas are non-circular 1.2 mm wide and 1.5 mm long oval shapes.

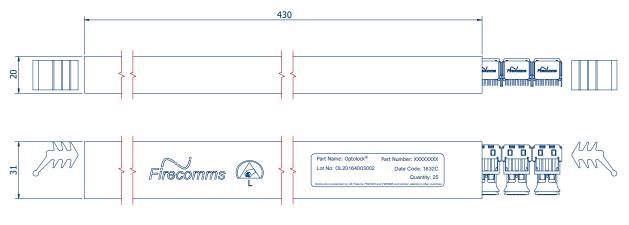

FIGURE 10 Packing tube for Firecomms OptoLock® Transceivers.

#### PART HANDLING

The transceivers are tested for handling in static-controlled assembly processes (HBM). Cleaning, degreasing and post solder washing should be carried out using standard solutions compatible with both plastics and the environment. For example, recommended solutions for degreasing are alcohols (methyl, isopropyl and isobutyl). Acetone, ethyl acetate, phenol or similar solution based products are not permitted.

In the soldering process, non-halogenated water soluble fluxes are recommended. These components are not suitable for use in reflow solder processes (infrared/vapor-phase reflow). The dust plug should remain in place during soldering, washing and drying processes to avoid contamination of the active optical area of each connector.

The Moisture Sensitivity Level (MSL) classification of this device is 2a according to JEDEC J-STD-020. The shelf life of an unopened MBB (Moisture Barrier Bag) is 24 months at < 40 °C and < 90 % R.H. Once the Moisture Barrier Bag is opened the devices can be either

- a) Stored in normal factory conditions < 30 °C and < 60 % R.H. for a maximum of 672 hours (4 Weeks) prior to soldering.

- b) Stored at < 10 % R.H. (Dry Cabinet).

#### **PACKING INFORMATION**

Components are packed in PVC anti-static tubes in moisture barrier bags. Bags should be opened only in static-controlled locations, and standard procedures should be followed for handling moisture sensitive components

| Components per Tube               |                     | 25      |

|-----------------------------------|---------------------|---------|

|                                   | Tube Length         | 430 mm  |

|                                   | Tube Width          | 31 mm   |

|                                   | Tube Height         | 20 mm   |

| Tubes per Bag                     |                     | 10      |

| Bags per Inner Carton             |                     | 1       |

|                                   | Inner Carton Length | 588 mm  |

|                                   | Inner Carton Width  | 147 mm  |

|                                   | Inner Carton Height | 84 mm   |

| Weight per Inner Carton, Complete |                     | 1.80 kg |

| Components per Inner Carton       |                     | 250     |

| Inner Cartons per Outer Carton    |                     | 4       |

|                                   | Outer Carton Length | 600 mm  |

|                                   | Outer Carton Width  | 310 mm  |

|                                   | Outer Carton Height | 195 mm  |

| Weight per Outer Carton, Complete |                     | 7.53 kg |

| Components per Outer Carton       |                     | 1000    |

For the most recent revision or further information please visit <u>www.firecomms.com</u> or contact the company directly at the following address, Firecomms Ltd, 2200 Airport Business Park, Cork, IRELAND. Copyright© 2004-2018 Firecomms. All rights reserved. Firecomms refers to Firecomms Limited and/or its subsidiaries. Firecomms assumes no responsibility for inaccuracies or omissions in the information contained in this document. Specifications are subject to change without notice. No patent rights are granted to any of the circuits described herein.

FB2M5KRR Revision B